# TECHNICAL MANUAL

# USERS MANUAL COMMUNICATION PROCESSOR MODEL IS/1900 TYPE AN/UYQ ( )

This manual contains material reproduced by permission of GTE/IS. Use, duplication, or disclosure for use outside the Government is not authorized.

HEADQUARTERS, DEPARTMENT OF THE ARMY

NOVEMBER 1979

# HE INQUIRTURS DEPLICATIONS OF THE ARM Vashington, DC, 30 November 1979

TM 11-7010.200-10.9-2, 30 November 1979, is published for the use of all concerned. This manual is a reprint of To 3185-4-525-15-1, 17 March 1978,

By Order of the Secretary of the Amer

E. C. MEYER General, United States hims Chief of Staff.

Offictal:

J. C. PENHLINGTON Major General, United States Amy The Adjutant General

DISTRIBUTION: Active Army

> 715G (1) WEATHENHD (1) USATHSCOM (2) TRAHOC (2) DATISOM (1) TECOM (1) OS Maj Gond (2) HISA (Ft Mornouth (21) himins (1) WASHES (10) Svc Golleges (1) HISMIR (1) USINERDALA (1) USAMERDAM (1) Ft Richardson (CERCON Ofc) (1) Fit Canson (5) Fi: Gillen (5)

Army Dep (4) except 133AD (10) S/AT/ (10) 1:0A) (1/1) CO CAHE 135/ Dep (1.) Sig Set Ull Dep (1) Units org under fol TOE: 29-134 (1) 29...(36 (1) 29 207 (2) 29 -610 (2) Acc: # 110497 (2) # # DO751 (1) # 30534 (1) # A0049 (1) " // SO392 (3) " / JOB 61 (10) # GN214 (2)

HG: NOTE

USANE HONE

For emplanation of abbreviations see, AR 510-50.

# **CONTENTS**

| <u>Para</u>             | <u>graph</u>                                                                                                                                                                                                                                                                     | Page                                                                                              |

|-------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------|

|                         | SECTION 1<br>INTRODUCTION                                                                                                                                                                                                                                                        |                                                                                                   |

| 1 . 1<br>1 . 2<br>1 . 3 | PURPOSE SCOPE DOCUMENTATION 1.3.1 Publications 1.3.2 Abbreviations and Conventions                                                                                                                                                                                               | 1-1<br>1-1<br>1-1<br>1-1<br>1-1                                                                   |

|                         | SECTION 2 DESCRIPTION                                                                                                                                                                                                                                                            |                                                                                                   |

| 2.2                     | 2.1.1 I/O Bus  2.1.1.1. Direct Program O/O Control 2.1.2 Priority Interrupt I/O Control 2.1.3 Direct Memory Access 2.1.4 General Specifications PHYSICAL DESCRIPTION 2.2.1 Cable J1/P1 2.2.2 Cable J2/P2 2.2.3 Cable J3/P3 2.2.4 Cable J4/P4 2.2.5 Cable J1/P12 2.2.6 Test Cable | 2-1 2-1 2-1 2-1 2-1 2-2 2-2 2-2 2-2 2-4 2-4 2-6 2-7 2-7 2-7 2-7 2-9 2-11 2-11 2-13 2-13 2-13 2-13 |

|                         | SECTION 3 PRINCIPLES OF OPERATION                                                                                                                                                                                                                                                |                                                                                                   |

| 3.1<br>3.2<br>3.3       | AUTOLOAD OPERATION 3.1.1 Control Panel Initiated Autoload 3.1.2 Power Panel Initiated Autoload 3.1.3 Blank Panel Initiated Autoload CONTROL OPERATIONS INPUT/OUPUT OPERATIONS 3.3.1 I/O Timing                                                                                   | 3-1<br>3-1<br>3-1<br>3-2<br>3-2<br>3-4<br>3-4                                                     |

|                         | 3.3.2 Input Data Transfer 3.3.3 Output Data Transfer                                                                                                                                                                                                                             | 3-4<br>3-5                                                                                        |

| Parag | grapn                                                                                                                                                                                            | Page                                     |

|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------|

| 3.4   | INTERRUPT OPERATIONS 3.4.1 Internal Interrupts 3.4.1.1 Power-Fail/Restart Interrupt 3.4.1.2 Instruction Trap Interrupt 3.4.1.3 Memory Protect Interrupt 3.4.1.4 Privileged Instruction Interrupt | 3-6<br>3-8<br>3-8<br>3-8<br>3-10<br>3-10 |

|       | 3.4.2 External Interrupts                                                                                                                                                                        | 3-11                                     |

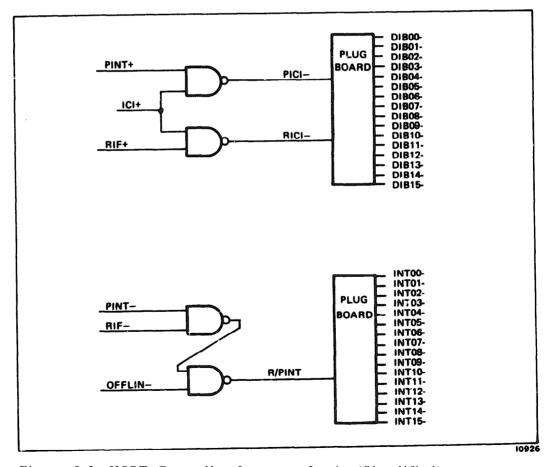

|       | 3.4.2.1 Individual External Interrupts 3.4.2.2 Common External Interrupts                                                                                                                        | 3-12<br>3-14                             |

| 3.5   | DIRECT DIRECT MEMORY ACCESS                                                                                                                                                                      | 3-14                                     |

| 3.3   | 3.5.1 DMA Selection Sequences                                                                                                                                                                    | 3-14                                     |

|       | 3.5.2 DMA Transfer Into Memory                                                                                                                                                                   | 3-16                                     |

|       | 3.5.3 DMA Transfer Out of Memory                                                                                                                                                                 | 3-16                                     |

|       | 3.5.4 DMA Single and Multiple Cycle Determination 3.5.5 DMA Control Priority Determination                                                                                                       | 3-16<br>3-18                             |

|       | SECTION 4                                                                                                                                                                                        |                                          |

|       | PROGRAMMING CONSIDERATIONS                                                                                                                                                                       |                                          |

| 4.1   | GENERAL                                                                                                                                                                                          | 4-1                                      |

| 4.2   | INSTRUCTIONS                                                                                                                                                                                     | 4 - 1<br>4 - 1                           |

|       | 4.2.1 I/O Instructions                                                                                                                                                                           | 4-1                                      |

|       | 4.2.1.1 EDF Instruction 4.2.1.2 ICI Instruction                                                                                                                                                  | 4-3                                      |

|       | 4.2.1.3 RDS Instruction                                                                                                                                                                          | 4-3                                      |

|       | 4.2.1.4 WTI Instruction                                                                                                                                                                          | 4-4                                      |

|       | 4.2.1.5 WTO Instruction                                                                                                                                                                          | 4-4                                      |

|       | 4.2.2 Interrupt Instructions                                                                                                                                                                     | 4-4                                      |

|       | 4.2.2.1 BRE Instruction                                                                                                                                                                          | 4-4<br>4-4                               |

|       | 4.2.2.2 BRI Instruction                                                                                                                                                                          | 4-4                                      |

|       | 4.2.2.3 LIB Instruction 4.2.2.4 SIE Instruction                                                                                                                                                  | 4-5                                      |

|       |                                                                                                                                                                                                  |                                          |

|       | SECTION 5<br>APPLICATIONS                                                                                                                                                                        |                                          |

| 5.1   | GENERAL                                                                                                                                                                                          | 5-1                                      |

| 5.2   | HIGH SPEED PAPER TAPE INTERFACE                                                                                                                                                                  | 5-1                                      |

|       | 5.2.1 General Description                                                                                                                                                                        | 5-1<br>5-1                               |

|       | 5.2.2 Program or Internal Control                                                                                                                                                                | 5-1                                      |

|       | 5.2.2.1 Input Control                                                                                                                                                                            | 5-3                                      |

|       | 5.2.2.2 Output Control                                                                                                                                                                           | 5-3                                      |

|       | 5.2.2.3 Input/Output Control. 5.2.2.4 Status Control.                                                                                                                                            | 5-3                                      |

|       |                                                                                                                                                                                                  | 5-4                                      |

|       | 5.2.3 Operator or External Control.<br>5.2.4 Sample Program                                                                                                                                      | 5-4                                      |

|       | 5.2.4 1 Program Listing                                                                                                                                                                          | 5-4                                      |

|       | 5 2 4 2 Program Description                                                                                                                                                                      | 5-5                                      |

| Parag | graph   |                         | Page |

|-------|---------|-------------------------|------|

| 5.3   | INTERRU | UPT PROGRAMMING         | 5-6  |

|       | 5.3.1   | General                 | 5-6  |

|       | 5.3.2   | Sample Program 1        | 5-6  |

|       |         | 5.3.2.1 Program Listing | 5-7  |

|       | 5 3 3   | Sample Program 2        | 5-7  |

|       | 3.3.3   | 5.3.3.1 Program Listing | 5-8  |

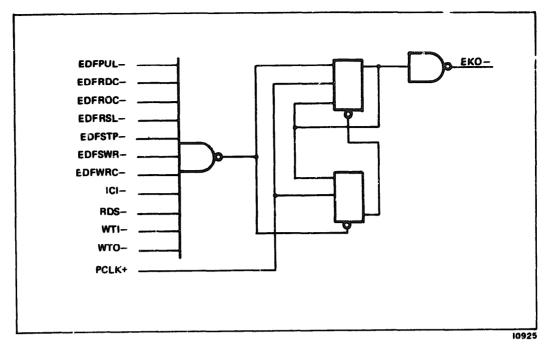

|       | 5 3 4   | EKO Logic and Control   | 5-8  |

# APPENDICES

| Appendix | Paragraph                                   | Page       |

|----------|---------------------------------------------|------------|

| A<br>R   | ASSIGNED I/O INSTRUCTION CODES WORD FORMATS | A-1<br>B-1 |

| D        | B 1 GENERAL                                 | B-1        |

# **TABLES**

| Table   | Title                                                        | Page  |

|---------|--------------------------------------------------------------|-------|

| 1-1     | Abbreviations.                                               | 1-2   |

| 2-1     | IS/1000 General Specifications                               | 2-3   |

| 2-2     | J1/P1 Signal Designations.                                   | 2-5   |

| 2-3     | J2/P2 Signal Designations.                                   | 2-5   |

| 2 - 4 a | J3/P3 Signal Designations, CPU to Control Panel,             | 2-6   |

| 2-4b    | J3/P3 Signal Designations, UCD to ED                         | 2-6   |

| 2-5     | J4/P4 Signal Designations.                                   | 2-7   |

| 2-6     | J12/P12 Signal Designations.                                 | 2-8   |

| 3-1     | Interrupt Memory and Device Address and Priority Assignments | 3 - 7 |

| 3-2     | DMA Mnemonics                                                | 3-15  |

| 5-1     | HSPT Controller Instruction Set.                             | 5-2   |

| 5-2     | HSPT Controller Interrupt Conditions                         | 5-3   |

| A-1     | Special Operations                                           | A-1   |

| A-2     | General I/O Operations                                       | A-1   |

| B-1     | IS/1000 Processor.                                           | B-2   |

| B-2     | Type 1 Expanded Performance Module                           | B-4   |

| B-3     | Type 2 Expanded Performance Module                           | B-5   |

| B-4     | High Capacity Removable Disc Controller.                     | B-6   |

| B-5     | Medium Capacity Disc Controller.                             | B-8   |

| B-6     | Rotating Drum Memory Controller.                             | B-10  |

| B-7     | Asynchronous Modem Multiplexer                               | B-11  |

| B-8     | Asynchronous Communication Adapter                           | B-13  |

| B-9     | Synchronous Modem Multiplexer.                               | B-15  |

| B-10    | Synchronous Communication Adapter.                           | B-16  |

| B-11    | Automatic Calling Unit Multiplexer                           | B-21  |

| B-12    | Block Check Unit                                             | B-21  |

| B-13    | Communication Transfer Unit.                                 | B-22  |

| B-14    | System Control Unit.                                         | B-28  |

| B-15    | Terminal Control Channel Interface Unit.                     | B-29  |

| B-16    | Tape Unit Channel Interface Unit                             | B-32  |

| B-17    | Input/Output Processor                                       | B-35  |

| B-18    | High Speed Paper Tape Reader/Punch Controller.               | B-36  |

| B-19    | Card Reader/Line Printer Controller.                         | B-36  |

| B-20    | Standard Card Punch Controller                               | B-37  |

| B-21    | Universal Magnetic Tape Controller                           | B-38  |

| B-22    | Utility Controller and Distributor and Utility Controller.   | B-40  |

# **ILLUSTRATIONS**

| Figure | Title                                                 | Page |

|--------|-------------------------------------------------------|------|

| 2-1    | I/O Bus Cable and Connector Assembly.                 | 2-4  |

| 2-2    | Interface 'Modification fox Board Test                | 2-8  |

| 2-3    | Control Panel Cabling                                 | 2-9  |

| 2-4    | Interface, Internal and External Cable Configuration. | 2-10 |

| 2-5    | Interface, Internal I/O Bus                           | 2-12 |

| 2-6    | Expanded Interface.                                   | 2-14 |

| 2-7    | Expansion Interface Logic                             | 2-15 |

| 3-1    | CPU Module Function Interface                         | 3-3  |

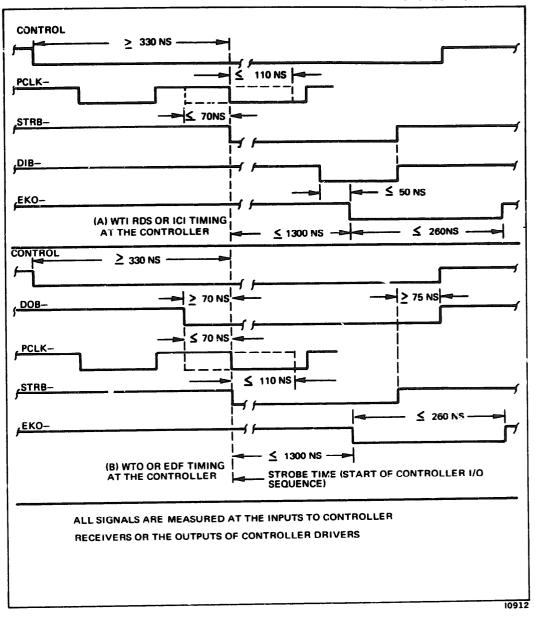

| 3-2    | I/O Sequence Timing at Controller                     | 3-5  |

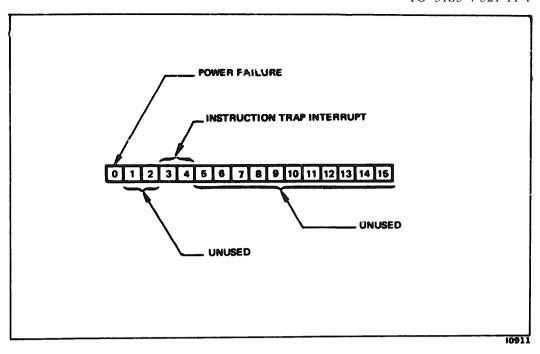

| 3-3    | CPU Module Status Word                                | 3-9  |

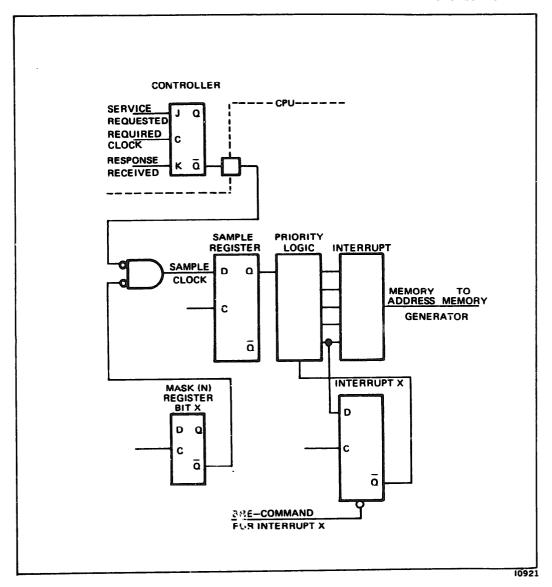

| 3 - 4  | Simplified Logic for External Interrupts              | 3-13 |

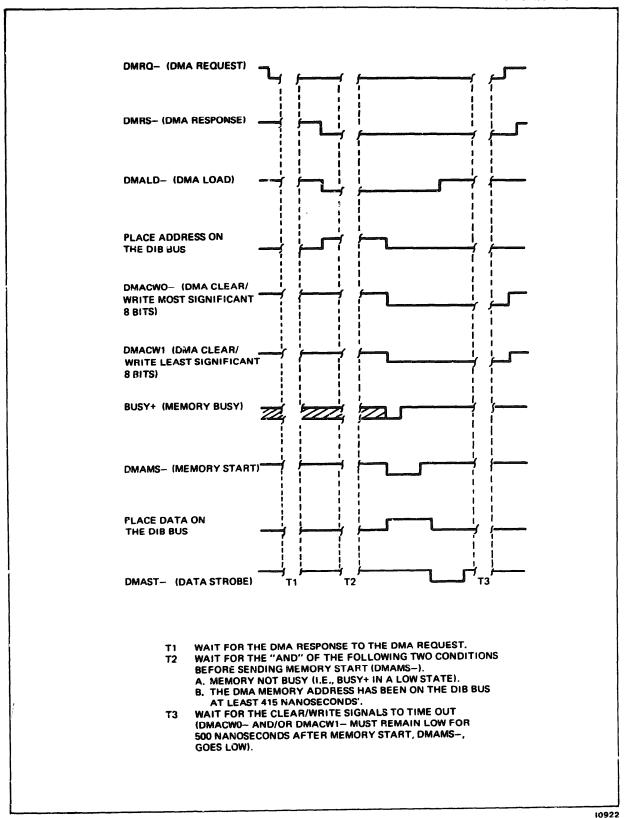

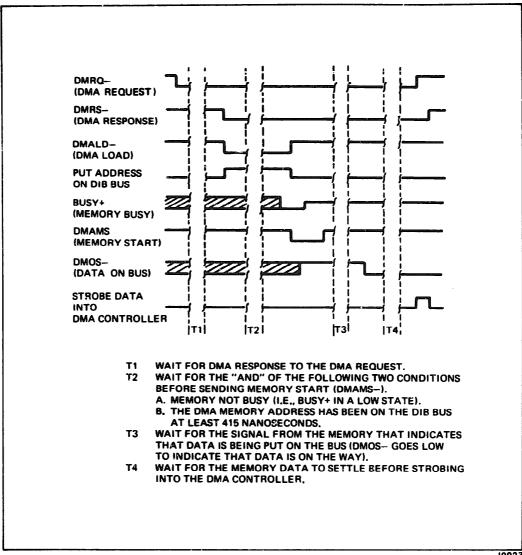

| 3-5    | DMA Write Operation Timing Diagram.                   | 3-17 |

| 3-6    | DMA Read Operation Timing Diagram                     | 3-18 |

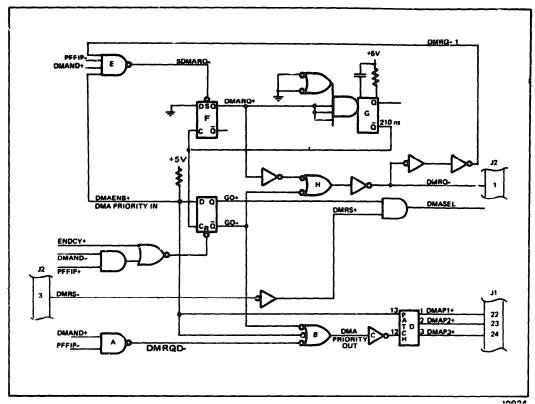

| 3 - 7  | DMA Priority Determination Logic.                     | 3-19 |

| 4 - 1  | Instruction Format                                    | 4-2  |

| 5-1    | HSPT Controller EKO Logic (Simplified).               | 5-9  |

| 5-2    | HSPT Controller Interrupt Logic (Simplified).         | 5-9  |

# SECTION 1 INTRODUCTION

#### 1.1 PURPOSE

This technical manual describes the operation principles of, and gives application information for, the standard input/output (I/O) bus, the priority interrupt scheme and the direct-memory-access (DMA) feature used in the GTE/IS IS/1000 Communications Processor.

#### 1.2 SCOPE

The information provided by this manual facilitates the design and programming of peripheral device controllers used in conjunction with the IS/1000 processor. As such, assumption is made that the person using this manual is skilled in state-of-the-art electronic and/or programming techniques, and has a thorough knowledge of solid-state computer logic implementation. A further requisite for the effective use of this manual is complete knowledge of the IS/1000 basic processor.

#### 1.3 DOCUMENTATION

#### 1.3.1 Publications

This manual supports all other manuals relating to the IS/1000 processor in general, but should be used specifically with the IS/1000 User's Manual, GTE/IS publication E0006.

#### 1.3.2 Abbreviations and Conventions

Table 1-1 defines the abbreviations used in this publication. The **followi**ng conventions are observed throughout the text:

- "\$" preceding a number signifies that it is in hexadecimal notation.

- The names of instructions are capitalized for easy identification.

- Signal mnemonics that appear on logic diagrams and panel nomenclature are reproduced in all upper-case characters.

- TELEPRINTER MESSAGES ARE REPRODUCED IN 1403 TYPE STYLE, AS SHOWN IN THIS EXAMPLE.

- ONE and ZERO are used in text to represent binary "1" and binary "0" bit conditions, respectively.

- Values represented in teleprinter (TTY) messages by letters are reproduced in Scribe type style, as shown here.

- Relative signal polarity is indicated by a sign suffixed to the mnemonic. For example: PLXHFC- (more negative signal; approximately +0.2 Vdc), PLXHFC+ (more positive signal; approximately +3.7 Vdc).

Table 1-1. Abbreviations

| Abbreviation | Meaning                                                             |

|--------------|---------------------------------------------------------------------|

| A            | Ampere.                                                             |

| đc           | Direct current.                                                     |

| DMA          | Direct memory access.                                               |

| DTL          | Diode-transistor lcgic.                                             |

| ED           | Expansion Distributor.                                              |

| F            | Farad.                                                              |

| GTE/IS       | General Telephone and Electronics Information Systems, Inc.         |

| hspt         | High-speed paper tape (reader).                                     |

| Hz           | Hertz.                                                              |

| IC           | Integrated circuic.                                                 |

| 1/0          | Input/output.                                                       |

| IOP          | I/O processor.                                                      |

| kHz          | Kilohertz.                                                          |

| mA           | Milliampere.                                                        |

| MHz          | Megahertz.                                                          |

| wV           | Millivolt.                                                          |

| ms           | Millisecond.                                                        |

| ns           | Nanosecond.                                                         |

| PC           | Printed circuit.                                                    |

| <b>p</b> F   | Picofarad.                                                          |

| Sync         | Synchronization.                                                    |

| TTL          | Transistor-transistor logic.                                        |

| TTY          | Teleprinter.                                                        |

| UCD          | Utility Controller and Distributor.                                 |

| us           | Microsecond.                                                        |

| USASCII      | United States of America Standard Code for Information Interchange. |

| Vac          | Volts, alturnating current.                                         |

| Vđc          | Volts, direct current.                                              |

| XPM          | Expanded Performance Module.                                        |

# SECTION 2 DESCRIPTION

#### 2.1 GENERAL

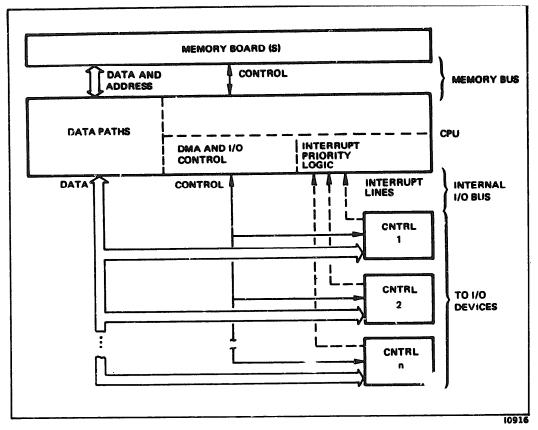

The interface provides a simple, standardized communication link through which information is exchanged within the IS/1000 processor system. The interface physically and electrically interconnects the processor, the memory, and various peripheral devices with their associated controllers. The channeling of information from one system entity to another is regulated by logically connecting and disconnecting the units according to a standardized set of logical conditions and timing criteria.

There are three types of interface operation:

- 1. The I/O bus, which channels information between the CPU and a peripheral device via the associated peripheral device controller.

- 2. The memory bus, which channels information between the CPU and the memory.

- 3. Direct memory access (DMA), which channels information between the memory and a peripheral device via the associated peripheral device controller.

#### 2.1.1 I/O Bus

The I/O bus connects the CPU to a peripheral device via a suitable controller. The purpose of the controller is to provide compatibility between the operational requirements of the peripheral device(s) and the logical and electrical criteria of the CPU. Although GTE/IS provides several standard controllers, a custom controller can readily be designed by GTE/IS for the IS/1000 user due to the straightforward logic of the I/O bus.

With a controller connected to the I/O bus, communication between the CPU and the peripheral device is program controlled, either directly and entirely by the program, or in combination with the priority interrupt system.

# 2.1.1.1 Direct Program I/O Control

Although the use of interrupts is generally adopted in I/O control, it is possible to have the program start a peripheral device, then make a periodic check on the status of the controller until a ready condition is indicated. The program can then transfer data in word or block segments at the proper rate. Under direct program I/O control, the program must determine the correct rate of data exchange and monitor controller readiness.

# 2.1.1.2 Priority Interrupt I/O Control

Once a peripheral device has been started via its associated controller, the CPU can resume processing until the peripheral device

#### TO 31S5-4-521-11-1

either has data for transmission or is ready to accept data. When the peripheral device requires servicing, the controller activates an interrupt line. The priority interrupt logic of the CPU causes the CPU to discontinue processing at the appropriate time to select and service the highest-priority interrupt pending. Data is transferred between the CPU and the controller during this interrupt service.

#### 2.1.2 Memory Bus

The memory bus, which connects the memory directly to the CPU, is an asynchronous interface. Under normal circumstances, the memory does not supply data or accept a new address as fast as the CPU requires. Under these conditions, the CPU suspends processing until the memory is ready for the required function.

# 2.1.3 Direct Memory Access

The DMA channel enables direct data transfers between the memory and the I/O bus. Although the DMA channel physically utilizes the cable connections comprising the I/O bus and the memory interface, it bypasses the CPU logically. Each data transfer requires one memory cycle.

The DMA channel functions independently of the program since there are no instructions to affect it. To use the DMA channel, the processor must condition the peripheral device via the I/O bus, while the peripheral device requesting direct memory access, must supply the necessary control signals and address information to the memory. An Input/Output Processor (IOP), GTE/IS Model 4540-01, is optionally available to simplify use of the DMA channel. The IOP supplies signals and sequences the memory address for all standard peripheral devices.

# 2.1.4 General Specifications

The general specifications for the IS/1000 interface are listed in Table 2-1.

#### 2.2 PHYSICAL DESCRIPTION

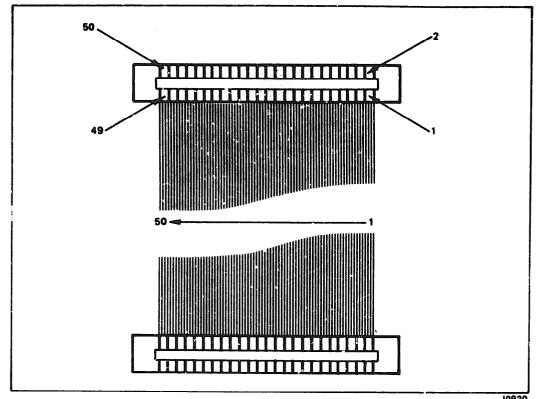

The signal interface consists of flat 50-conductor ribbon cables of various lengths, which plug onto the logic boards with dual-25 quick-connect press-on type edge connectors. The edge connectors terminate or branch off the cables so that one cable can have multiple connectors and interconnect several logic boards.

All interface logic is TTL implemented, using the latest MSI technology whenever possible. Each board contains its own driver/receiver logic for the signal lines that it uses. The logic implementing the priority interrupt system and the interrupt mask, is contained in the CPU assembly.

The cable line and connector pin numbering schemes are given in Figure 2-1.

| Characteristic             | Specification                                                                                                            |

|----------------------------|--------------------------------------------------------------------------------------------------------------------------|

| Functional                 |                                                                                                                          |

| Word Length                |                                                                                                                          |

| Instruction                | 16 or 32 bits.                                                                                                           |

| Data                       | 16 bits.                                                                                                                 |

| Interrupts                 |                                                                                                                          |

| Internal                   | <pre>2 interrupts with separate priority levels (4 interrupts when an XPM option is used).</pre>                         |

| External                   | 8 priority levels (expandable to 16 using an XPM option).                                                                |

| Electrical                 |                                                                                                                          |

| I/O Interface              |                                                                                                                          |

| Standard                   | Shared by up to 64 addressable device controllers; data transfer rate up to 77,000 words per second (program dependent). |

| Logic Levels               |                                                                                                                          |

| High                       |                                                                                                                          |

| TTL                        | +3.7 ± 1.7 V.                                                                                                            |

| Low                        |                                                                                                                          |

| TTL                        | +0.2 ± 0.6 V.                                                                                                            |

| Environmental              |                                                                                                                          |

| Temperature                |                                                                                                                          |

| Storage                    | -25° C to +75° C.                                                                                                        |

| Operating                  | 00 C to +550 C.                                                                                                          |

| Humidity                   | 0 to 90% relative without condensation.                                                                                  |

| Controller Circuitry       |                                                                                                                          |

| Input (CPU to Controller)  | TTL (Medium Speed recommended).                                                                                          |

| Output (Controller to CPU) | TTL Open Collector                                                                                                       |

Figure 2-1. I/O Bus Cable and Connector Assembly

Physically the interface comprises the following cable assemblies:

- Cable assembly J1/P1.

- Cable assembly J2/P2.

- Cable assembly J3/P3.

- Cable assembly J4/P4.

- Cable assembly J12/P12.

- Text cable assembly, P/N 102156.

# 2.2.1 Cable J1/P1

The J1/P1 cable is a custom manufactured cable (Table 2-2). The J1/P1 cable has an edge connector for the control panel, one for the CPU and one for each of the peripheral controllers in the system. All connectors on the cable are designated P1 and plug onto corresponding J1 designated PC edge contact strips on the logic boards. In single or dual chassis systems, the cable terminates in the control panel and in the last controller of the system. In a multi-chassis system configuration, the cable terminates in the control panel and in the Utility Controller and Distributor (UCD) board, located in the second chassis. The J1/P1 cable, together with its matched counterpart, the J2/P2 cable, constitutes the internal I/O bus.

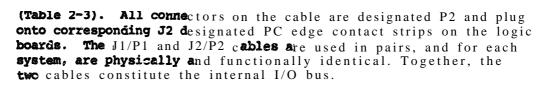

#### 2.2.2 Cable J2/P2

The J2/P2 cable is, like the J1/P1 cable, custom configured to fit a specific system and therefore, may differ from one system to another

Table 2-2. J1/P1 Signal Designations

| Signal                                                                                                                                                | Signal                                                                                                          | Signal                                                                                                                                       | Signal                                                                                                              | Signal                                                                                                                                       | Signal                                                                                                                                                                  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Line                                                                                                                                                  | Mnemonic                                                                                                        | Line                                                                                                                                         | Mnemonic                                                                                                            | Line                                                                                                                                         | Mnemonic                                                                                                                                                                |

| J1-01<br>J1-02<br>J1-03<br>J1-04<br>J1-05<br>J1-06<br>J1-07<br>J1-08<br>J1-09<br>J1-10<br>J1-11<br>J1-12<br>J1-13<br>J1-14<br>J1-15<br>J1-16<br>J1-17 | DIB06- DIB14- DIB04- DIB01- DIB05- DIB15- DIB13- DIB10- DIB11- DIB07- DIB02- DIB03- DIB05- DIB08- DIB09- GROUND | J1-18<br>J1-19<br>J1-20<br>J1-21<br>J1-22<br>J1-23<br>J1-24<br>J1-25<br>J1-26<br>J1-27<br>J1-28<br>J1-29<br>J1-30<br>J1-31<br>J1-32<br>J1-33 | EKO- GROUND STRB- GROUND DMAP1+ GROUND INT15- GROUND DMAP2+ GROUND INT13- GROUND INT12- GROUND INT12- GROUND INT10- | J1-35<br>J1-36<br>J1-37<br>J1-38<br>J1-39<br>J1-40<br>J1-41<br>J1-42<br>J1-43<br>J1-44<br>J1-45<br>J1-46<br>J1-47<br>J1-48<br>J1-49<br>J1-50 | GROUND INT11 GROUND INT09 GROUND INT14 GROUND DMAP3+ GROUND PCLK GROUND DA05 GROUND DA05 GROUND DA01 GROUND DA01 GROUND DA01 GROUND DA01 GROUND DA01 GROUND DA01 GROUND |

Table 2-3. J2/P2 Signal Designations

| Signal                                                                                                                                       | Signal                                                                                                              | Signal                                                                                                | Signal                                                                                                                 | Signal                                                                                                                                       | Signal                                                                                                |

|----------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------|

| Line                                                                                                                                         | Mnemonic                                                                                                            | Line                                                                                                  | Mnemonic                                                                                                               | Line                                                                                                                                         | Mnemonis                                                                                              |

| J2-01<br>J2-02<br>J2-03<br>J2-04<br>J2-05<br>J2-06<br>J2-07<br>J2-08<br>J2-09<br>J2-10<br>J2-11<br>J2-12<br>J2-13<br>J2-14<br>J2-15<br>J2-16 | DMRQ- GROUND DMRS- GROUND SYRST- GROUND DMALD- GROUND SPARE DOB11- DOB13- DOB12- DOB07- DOB04- DOB05- DOB06- DOB01- | J2-18 J2-19 J2-20 J2-21 J2-22 J2-23 J2-24 J2-25 J2-26 J2-27 J2-28 J2-29 J2-30 J2-31 J2-32 J2-33 J2-34 | DOBO2- DOBO9- DOBO9- DOBO3- DOB10- DOB14- DOB08- DOB15- GROUND BUSY+ GROUND DMOS- PRLD- GROUND DMACW1- GROUN': DMACW0- | J2-35<br>J2-36<br>J2-37<br>J2-38<br>J2-39<br>J2-40<br>J2-41<br>J2-42<br>J2-43<br>J2-44<br>J2-45<br>J2-46<br>J2-47<br>J2-48<br>J2-49<br>J2-50 | GROUND DMAMS- GROUND DMAST- GROUND ALOAD+ PFFIP- ALOAD- GROUND DA00- DA02- DA03- DA04- KF0- KF1- KF2- |

# 2.2.3 Cable J3/P3

The J3/P3 cable comes in two versions, a standard cable and a custom designed rable (Tables 2-4a and 2-4b). With either version, the connectors on the cable are designated P3 and plug onto corresponding J3 designated PC edge contact strips on the logic boards. In all systems, regardless of configuration, the standard J3/P3 cable connects the CPU to the control panel (Table 2-4a). In expanded system configurations of more than two chassis, the custom J3/P3 cable connects the UCD in

Table 2-4a. J3/P3 Signal Designations, CPU to Control Panel

| J3-01         SCTFP-         J3-18         BEQ-         J3-35         GROUND           J3-02         FPIRO2         J3-19         GROUND         J3-36         MSW-           J3-03         GROUND         J3-20         FPIRO1-         J3-37         GROUND           J3-04         BOVF         J3-21         GROUND         J3-38         MEDI-           J3-05         GROUND         J3-22         KSSW3+         J3-39         GROUND           J3-06         FPIRO0         J3-23         GROUND         J3-40         GROUND           J3-07         GROUND         J3-24         KSSW1+         J3-41         GROUND           J3-08         FPIRO3         J3-25         GROUND         J3-42         FPR+           J3-09         GROUND         J3-26         KSSW0+         J3-43         GROUND |                                                                                                       |                                                                                                                            |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------|

| J3-10         GROUND         J3-27         GROUND         J3-44         GROUND           J3-11         GROUND         J3-28         RUNLTE-         J3-45         GROUND           J3-12         BLT-         J3-29         GROUND         J3-46         PSW-           J3-13         GROUND         J3-30         RUNSW-         J3-47         GROUND           J3-14         BGT-         J3-31         GROUND         J3-48         INITE           J3-15         GROUND         J3-32         STEPSW-         J3-49         GROUND           J3-16         KSSW2+         J3-33         GROUND         J3-50         RSMRI                                                                                                                                                                                 | J3-04 J3-05 J3-06 FPI J3-07 GRO J3-08 FPI J3-09 GRO J3-10 GRO J3-11 GRO J3-12 BLT J3-13 GRO J3-14 BGT | J3-02<br>J3-03<br>J3-04<br>J3-05<br>J3-06<br>J3-07<br>J3-08<br>J3-09<br>J3-10<br>J3-11<br>J3-12<br>J3-13<br>J3-14<br>J3-15 |

Table 2-4b. J3/P3 Signal Designations, UCD to ED

| Signal                                                                                                                                                | Signal                                                                                                                                                     | Signal                                                                                                                                                | Signal                                                                                                                                | Signal                                                                                                                                       | Signal                                                                                                                              |

|-------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------|

| Line                                                                                                                                                  | Mnemonic                                                                                                                                                   | Line                                                                                                                                                  | Mnemonic                                                                                                                              | Line                                                                                                                                         | Mnemonic                                                                                                                            |

| J3-01<br>J3-02<br>J3-03<br>J3-04<br>J3-05<br>J3-06<br>J3-07<br>J3-08<br>J3-09<br>J3-10<br>J3-11<br>J3-12<br>J3-13<br>J3-14<br>J3-15<br>J3-16<br>J3-17 | DEKO-R DEKO- DINT15-R DINT15- DINT14-R DINT14- DINT13-R DINT13-R DINT12-R DINT12-R DINT11-R DINT11-R DINT11-C DINT10-R DINT10-R DINT09-R DINT09-R DINT09-R | J3-18<br>J3-19<br>J3-20<br>J3-21<br>J3-22<br>J3-23<br>J3-24<br>J3-25<br>J3-26<br>J3-27<br>J3-28<br>J3-29<br>J3-30<br>J3-31<br>J3-32<br>J3-33<br>J3-34 | DINTO8- DDB00-R DDB01-R DDB01-R DDB01- DDB02-R DDB02- DDB03-R DDB03-R DDB04-R DDB04-R DDB05-R DDB05-R DDB06-R DDB06-R DDB07-R DDB07-R | J2-35<br>J3-36<br>J3-37<br>J3-38<br>J3-39<br>J3-40<br>J3-41<br>J3-42<br>J3-43<br>J3-44<br>J3-45<br>J3-46<br>J3-47<br>J3-48<br>J3-29<br>J3-50 | DDB08-R DDB09-R DDB09-R DDB09- DDB10-R DDB10- DDB11-R DDB11- DDB12-R DDB12- DDB13-R DDB13-R DDB14-R DDB14-R DDB14-R DDB15-R DDB15-R |

in the second chassis to the Expansion Distributor(s) in successive chassis (Table 2-4b). Together with its matched counterpart, cable J4/P4, the custom J3/P3 cable constitutes the external I/O bus in expanded system configurations.

# 2.2.4 Cable J4/P4

The J4/P4 cable is a custom designed cable (Table 2-5). All connectors on the cable are designated P4 and plug onto corresponding J4 designated PC edge contact strips on the logic boards. In all systems, regardless of configuration, one J4/P4 cable interconnects the CPU and all memory boards in the system. Additionally, in expanded system configurations of three or more chassis, a second J4/P4 cable is used to connect the UCD in the second chassis to the Expansion Distributor(s) in successive chassis. The J3/P3 and J4/P4 cables are used in matched pairs and for each particular system, are physically and functionally identical. Together they constitute the external I/O bus in expanded system configurations.

# 2.2.5 Cable J12/P12

The J12/P12 cable is a custom cable used only in system configurations that comprise more than two chassis (Table 2-6). The connectors on the cable are designated as P12 and plug onto the corresponding J12 designated PC edge contact strips of the UCD and Expansion Distributor boards, where the cable constitutes the DMA expansion bus.

#### 2.2.6 Test Cable

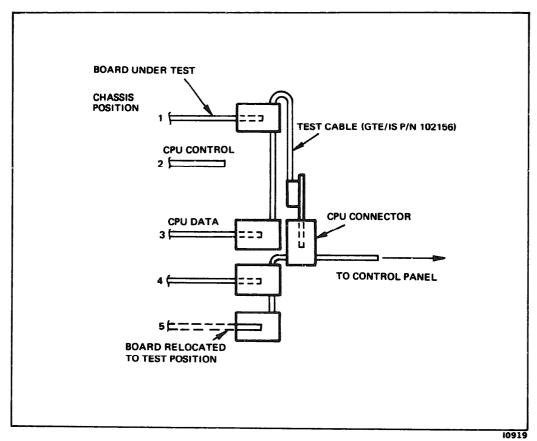

The test cable enables temporary modification of the interface cabling to facilitate the checkout of a logic board, placed in the test position of the main chassis. (Figure 2-2).

Table 2-5. J4/P4 Signal Designations

| Signal                                                                                                                                                | Signal                                                                                                                                                                                                                                                           | Signal                                                                                                | Signal                                                                                                                  | Signal                                                                                                                                                | Signal                                                                                                                                                         |

|-------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Line                                                                                                                                                  | Mnemonic                                                                                                                                                                                                                                                         | Line                                                                                                  | Mnemonic                                                                                                                | Line                                                                                                                                                  | Mnemonic                                                                                                                                                       |

| J4-01<br>J4-02<br>J4-03<br>J4-04<br>J4-05<br>J4-06<br>J4-07<br>J4-08<br>J4-09<br>J4-10<br>J4-11<br>J4-12<br>J4-13<br>J4-14<br>J4-15<br>J4-16<br>J4-17 | DPFFIP-R DPFCIP- DDAJO-R DDAJO-R DDAO1-R DDAO1-R DDAO2-R DDAO2-R DDAO3-R DDAO3-R DDAO4-R DDAO4-R DDAO5-R | J4-18 J4-19 J4-20 J4-21 J4-22 J4-23 J4-24 J4-25 J4-26 J4-27 J4-28 J4-29 J4-30 J4-31 J4-32 J4-33 J4-34 | DKF1- DKF2-R DKF2- DOF0-R DOF0- DOF1-R DOF1- DOF2-R DCF2- DPCLK+R DPCLK+ DSTRB+R DSTRB+ DSYRST+R DSYRST+ DPRLD+R DPRLD+ | J4-35<br>J4-36<br>J4-37<br>J4-38<br>J4-39<br>J4-40<br>J4-41<br>J4-42<br>J4-43<br>J4-44<br>J4-45<br>J4-45<br>J4-46<br>J4-47<br>J4-48<br>J4-49<br>J4-50 | DINTO7-R DINTO7- DINTO6-R DINTO6-R DINTO5-R DINTO5- DINTO4-R DINTO4-R DINTO3-R DINTO3-R DINTO3- DINTO2-R DINTO2-R DINTO1-R DINTO1-R DINTO1-R DINTO1-R DINTO0-R |

Table 2-6. J12/P12 Signal Designations

| Signal<br>Line | Signal<br>Mnemonic | Signal<br>Line | Signal<br>Mnemonic | Signal<br>Line | Signal<br>Mnemonic ' |

|----------------|--------------------|----------------|--------------------|----------------|----------------------|

| J12-01         | DDMAP3+R           | J12-11         | DDMALD-            | J12-21         | DDMAST-              |

| J12-02         | DDMAP3+            | J12-12         | DDMALD-R           | J12-22         | DDMAST-R             |

| J12-03         | DDMAP2+R           | J12-13         | DDMRS-             | J12-23         | DDMAS-               |

| J12-04         | DDMAP2+            | J12-14         | DDMRS-R            | J12-24         | DDMAS-R              |

| J12-05         | DDMAP1+R           | J12-15         | DDMRQ-             | J12-25         | DDMACW1-             |

| J12-06         | DDMAP1+            | J12-16         | DDMRQ-R            | J12-26         | DDMACW1-R            |

| J12-07         | DDMOS-R            | J12-17         | DALOAD+            | J12-27         | DDMA:TWO-            |

| J12-08         | DDMOS-             | J12-18         | DALOAD+R           | J12-28         | DDMACWO-R            |

| J12-09         | DBUSY-R            | J12-19         | DALOAD-            |                |                      |

| J12-10         | DBUSY-             | J12-20         | DALOAD-R           |                |                      |

Figure 2-2. Interface Modification for Board Test

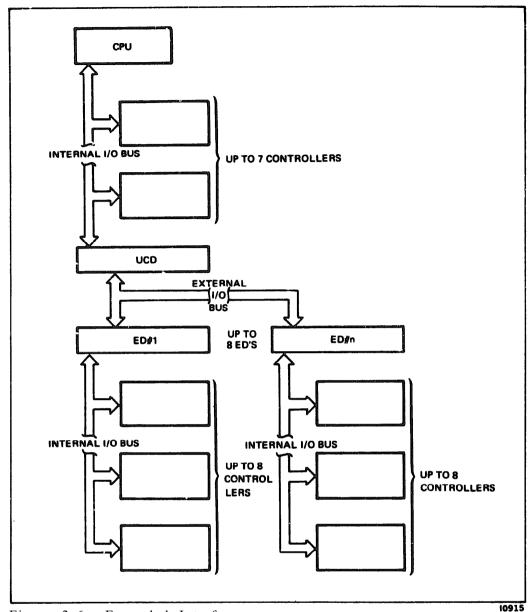

All communications and data transfers within the IS/1000 Processor system take place over the interface structure. All interface lines are connected to all controllers in parallel; however, only one controller at a time may use the lines. The CPU can drive 14 inches of I/O bus and up to eight peripheral device controllers or seven controllers and a Utility Controller and Distributor (UCD). If more than eight controllers are required by the system, or if the controllers are located more than 14 inches away from the CPU, a UCD must be used to buffer the I/O bus and to transfer I/O information to or from an Expansion Distributor (ED). A UCD can handle up to eight EDs or 25 feet of I/O bus. Each ED in turn can drive up to eight peripheral device controllers.

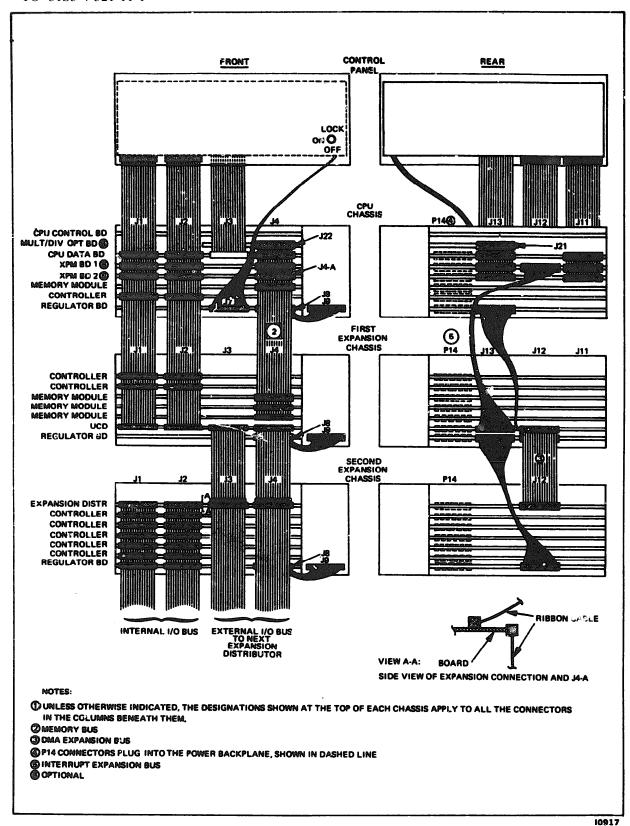

Functionally the interface comprises the following channels:

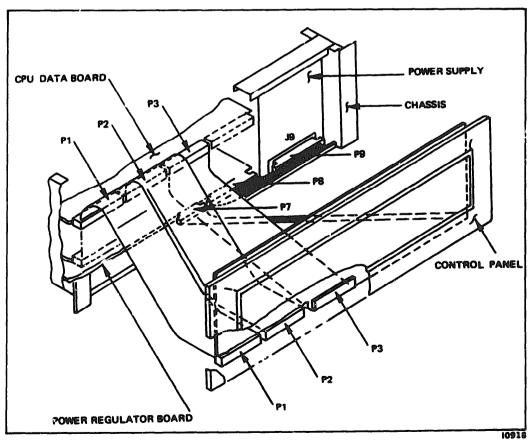

- CPU to Control Panel. This channel is constituted by the J3/P3 cable and portions of the J1/P1 and J2/P2 cables. (Figure 2-3). See Tables 2-2 and 2-3 for signal line designations.

- CPU to memory. This channel is constituted **by** the J4/P4 cable. (Figure 2-4). See Table 2-5 for si**gna**l line designations.

Figure 2-3. Control Panel Cabling

Figure 2-4. Internal and External Cable Configuration

- CPU to peripheral device controllers. These channels are constituted by the Jl/Pl and J2/P2 cables in system configurations with standard interface; additionally, by cables J3/P3 and J4/P4 in system configurations with expansion interfaces (Figure 2-4). See Tables 2-2 thru 2-6 for signal line designations.

- Memory to peripheral device controllers, i-e., DMA. This channel is established by cables J1/P1, J2/P2, J3/P3 and J4/P4 in system configurations with standard interface; additionally, by cable J12/P12 in system configurations with expansion interfaces (Figure 2-4). See Tables 2-2 thru 2-6 for signal line designations.

In systems comprised of three or more chassis, the interface is **extended with an** expansion or external I/O bus. In this case the **use of a UCD wor**king in 'conjunction with from one to eight EDs, is required.

Regardless of system configuration, the heart of the interface communication concept is the priority interrupt scheme and its effective use during  $I \setminus O$  operations.

For I/O operations with peripheral devices capable of data transfer rates of one million words per second and more, the DMA channel is available. The direct memory access is accomplished over the existing interface cable system, through a functional channel created by special logic.

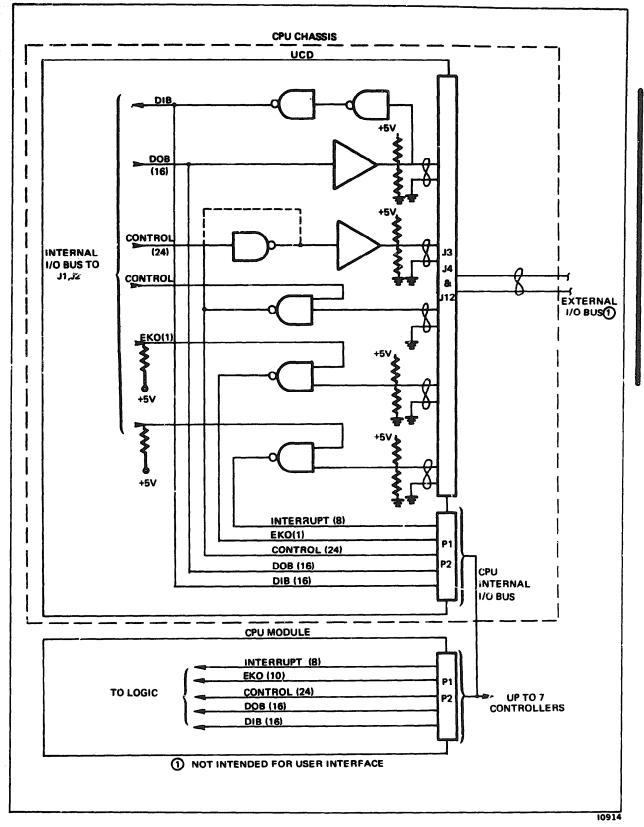

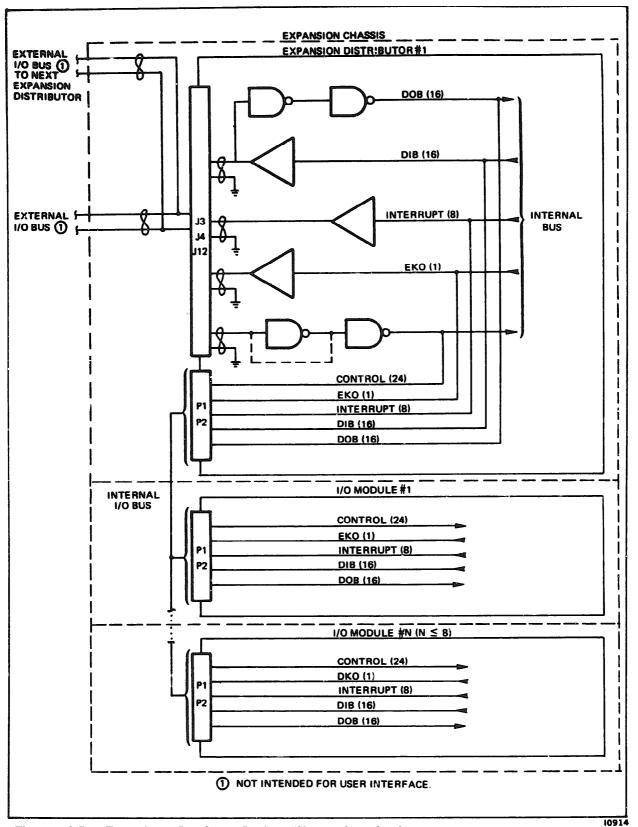

#### 2.3.1 Internal I/O Bus

All peripheral device controllers are connected to the internal I/O bus. The output lines of the internal I/O bus are originated, and the input lines terminated, by the I/O section in the CPU or in the ED.

The internal I/O lines, originating or terminating in the CPU assembly, are shown in Figure 2-5, and fall in three categories:

- Control signals.

- Interrupt signals.

- Data.

# 2.3.1.1 Control Signals

Control signals provide information to the controllers as to the type of function to be performed. Part of the instruction specifies the controller being addressed by the I/O instruction. The other parts of the instruction, are the K and O fields. The K-field defines the class of the instruction, the O-field defines the specific function to be performed for the particular instruction class specified by the K-field.

Figure 2-5. Interface, Internal I/O Bus

A strobe signal is used to enable the controller to accept the decoded command information, to transfer data in or out, or to initiate execution of a function.

The CPU provides a free-running 4-MHz clock for use by some controllers. The clock is not synchronous with the regular CPU clock **but rather wi**th the strobe signal.

A system reset is generated during power-up and power-down sequences, and when the RESET switch on the control panel is pressed while the CPU is in the Halt mode. The latter Reset condition causes all controllers to finalize current activity and become ready to accept new Commands, all peripheral devices to be halted and all status flags to be reset (except those requiring operator intervention).

**Autoloa**d signals are provided for use when the autoload function is **to be a**ctivated by peripheral devices using the I/O bus. The autoload condition causes execution of a special sequence that transfers a **program from a** ROM in the CPU to the memory **and starts execution** of that program. An autoload can be initiated in three ways:

- Control panel initiated autoload.

- Power panel initiated autoload.

- Blank panel initiated autoload.

# 2.3.1.2 Interrupt Lines

The I/O bus contains special lines for the eight regular external interrupts. Through use of an optional Expanded Performance Module (XPM) the number of lines can be functionally increased to 16. This is accomplished strictly through enhancement logic; physically, the number of lines on the internal I/O bus remains eight.

# 2.3.1.3 Data Lines

Output data is transferred from the CPU to the controllers via the Data Out bus lines. Input data is transferred from the controllers to the CPU via the Data In bus lines.

# 2.3.2 External I/O Bus

The external I/O bus is used to extend the physical length of the I/O bus and to provide the ability to attach up to eight EDs. The external I/O bus is not intended for peripheral device controller interfaces because of the critical drive and termination requirements. The external I/O bus originates in the UCD.

Line drivers and receivers are provided in the UCD and the EDs to maintain the logic levels and permit a fanout of eight loads on each line.

The external I/O bus may extend up to 25 feet in length. Since up to six controller boards can be installed in an expansion chassis that is 7 inches high, the standard I/O bus length is ample (Figures 2-5 and 2-6). Logic implementation of the I/O bus expansion feature is shown in Figure 2-7.

#### 2.3.3 Priority Interrupt System

An interrupt is generated when a peripheral device or a system function requires attention by the CPU. Interrupt sources are given interrupt priorities on the basis of importance and data transfer rate. Interrupt sources can both be external and internal to the CPU assembly. Internal interrupts are associated with automatic functions such as power failure detection and error conditions. External interrupts are associated with peripheral device servicing.

The priority interrupt system has control logic for:

- Active interrupt storage.

- Interrupt enable/disable.

- Interrupt recognition.

- Priority recognition.

- Priority selection.

- Generation of interrupt trap addresses.

Figure 2-6. Expanded Interface

The internal interrupts which are associated with the CPU have the following priorities, (0 is highest).

- 0. **Powe**r fail/restart.

- 1. Instruction trap.

- 2. **M**emory protect\*.

- 3. Privileged instruction interrupt\*.

\*XPMoption

Figure 2-7. Expansion Interface Logic (Sheet 1 of 2)

2-15

Figure 2-7. Expansion Interface Logic (Sheet 2 of 2)

The external interrupts have the following priorities (0 is highest).

- 0. General purpose\*.

- 1. General purpose\*.

- 2. General purpose\*.

- 3. General purpose\*.

- 4. General purpose\*.

- 5. General purpose\*.

- 6. General purpose\*.

- 7. General purpose\*.

- 8. General purpose.

- 9. General purpose.

- 10. General purpose.

- 11. General purpose.

- 12. General purpose.

- 13. General purpose.

- 14. Teleprinter.

- 15. General purpose.

NOTE: The controller can be patched to only eight-interrupts through patches on the controller board. The expansion to sixteen interrupts is provided through patches on the ED.

Internal interrupts have priority over external interrupts.

When two or more interrupts of any kind are active, priority logic in the CPU selects the appropriate interrupt for servicing. The logic also enables higher-priority interrupts to interrupt lower-priority interrupts in the process of being serviced, without loss of the lower priority status. Peripheral device controllers contain plugboards to establish the address and interrupt(s) of that device, with each interrupt patched for a specific priority level. The plugboards enable the ready reassignment of priority level or changing of the address at any time without etch pattern modifications. It is not necessary that the interrupt number coincides with the device number, but generally these numbers do correspond.

When two or more peripheral devices share a single interrupt line, they can be considered as having a level of priority within a level. Their priority is determined first by the relative position of the shaded interrupt line in the priority interrupt system, and second, by the priority established by the subroutine that services the

#### TO 31S5-4-521-11-1

shared interrupt. For those controllers that can share an interrupt, a plugboard is provided in the controller to select which data line is to respond to the ICI (interrogate common interrupt) I/O instruction.

As many as 16 peripheral devices can share any one of four common interrupt lines. Any combination of four interrupt lines may be used as common interrupts. The two most-significant bits of the peripheral device address are decoded for the ICI instruction. Thus, four distinct codes are available for selecting one of four interrupt lines.

# 2.3.4 Direct Memory Access

Through the DMA channel, direct data transfers between the memory and the I/O bus are made possible. Each data transfer requires one memory cycle of 750 ns for a maximum transfer rate of 1.33 MHz. However, due to inherent delays, the practical data transfer rate is 1.1 MHz\*. When the data transfer rate falls below 1.1 MHz\*, the DMA channel could free the CPU to enable processing of program instructions. To use the DMA channel, the processor must condition the peripheral device via the I/O bus. Then, when the peripheral device requires service, it requests access to the memory via a DMA request line.

At the beginning of every memory cycle, the processor synchronizes and recognizes any requests for direct memory access that are being made. This assures a no longer than 750-ns wait for a DMA cycle and as long as the DMA request line remains active, every memory cycle is available. However, delays longer than 750 ns are possible, when:

- Another peripheral device is using the DMA channel.

- The CPU has a power failure.

- An I/O instruction is being executed, since the same I/O bus is used for both, ordinary input/output and DMA operations.

# SECTION 3 PRINCIPLES OF OPERATION

# 3.1 AUTOLOAD OPERATION

Autoload signals, ALOAD+ and ALOAD- are provided for use when the autoload function is to be activated by devices on the I/O bus. Autoload causes execution of a special sequence that transfers a program from a ROM in the CPU to the memory and starts execution of that program. An autoload operation may be initiated in three ways:

- Control Panel Autoload.

- Power Panel Autoload.

- Blank Panel Autoload.

#### 3.1.1 Control Panel Initiated Autoload

With the control panel connected and the CPU in the Halt mode, the autoload function can be activated in one of **two** ways. If the key on the front panel is in the ON position, the load button on the control panel activates the autoload function when it is pressed and released. If the key on the front panel is in the LOCK position, the autoload function is activated via the I/O bus if term ALOAD+ goes high and term ALOAD- goes low simultaneously, for approximately 10 us. If the autoload operation is to be initiated via the I/O has and from the control panel as well, and it is desired to operate autoload from the front panel, the LOAD switch on the control panel must have additional controls, corresponding to the key on the control panel that disables the I/O bus switch controls of ALOAD+ and ALOAD-. Therefore, if the autoload operation is enabled simultaneously by key functions from the control panel and the I/O bus, it can not be activated by both, but only by one of the key functions.

# 3.1.2 Power Panel Initiated Autoload

The power panel autoload has the same functions and interlocks as the control panel, but in addition it brings up term SYRST- (system reset) which resets the CPU and all peripheral device controllers when the autoload function is activated, i.e., terms ALOAD+ and ALOAD- go true. This reset operation is a necessity since the power panel has only one switch, i.e., LOAD '(autoload). This switch must reset the CPU and all controllers. The following functions occur when the LOAD switch is activated, with the power panel connected to the CPU:

- Activate Autoload.

- Reset I/O

- Reset CPU.

The activation of the autoload function from the power panel or via the I/O bus is not synchronized with the CPU timing. Therefore, if the CPU is executing programs when autoload is activated, the

resetting of the CPU will probably alter register contents in the CPU. The memory interface is so designed that resetting the CPU should not affect the reading of data from memory but if the CPU is in the middle of a write into memory operation when it is reset, the data that is written into the memory can not be assumed to be correct.

#### 3.1.3 Blank Panel Initiated Autoload

Since the CPU does not require the control panel nor the power panel to operate, a blank panel may be used with it. The autoload is then controlled exclusively from the I/O bus. This eliminates the interlocking concept but still enables the CPU and I/O controllers to be reset. The activation of an autoload operation via the I/O bus is not synohronized with the CPU timing, therefore, resetting of the CPU will probably alter the contents of some registers in the CPU. The memory interface is be signed so that resetting of the CPU will not affect data already stored in memory but data that is being stored may be altered.

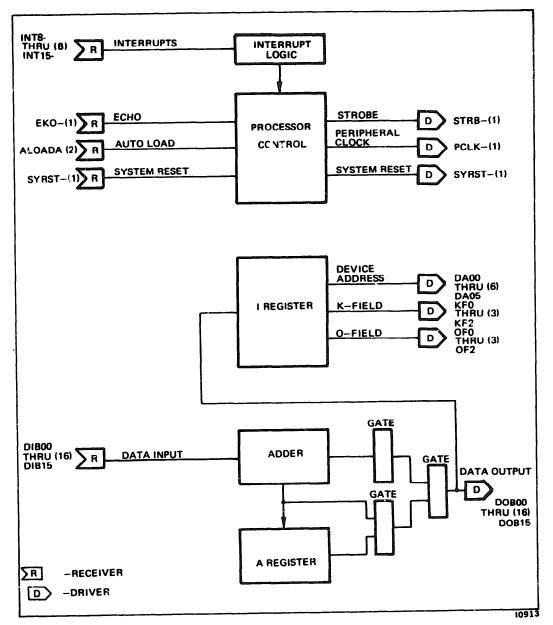

# 3.2 CONTROL OPERATIONS

The CPU communicates **wi**th all peripheral devices and their associated controllers, via the I/O **bus** structure (Figure 3-1). When the CPU is ready to communicate **with** a controller, the CPU places the desired controller address and **command** signals plus data (if applicable) on the I/O bus. Only the addressed controller recognizes the address and responds to the instruction.

The device address of the controller comes from bits 10 thru 15 of the I Register. The device address is sent to indicate the particular device controller being addressed by the I/O instruction. All controllers decode the device address, but only the addressed controller can respond. If an I/O controller is addressed but does not respond by sending an echo signal, the CPU does a Branch-and-Store-P (BSP) instruction to the address specified by the second word of the I/O instruction. The I/O bus mnemonics for the device address bits are DA00 thru DA05, corresponding to I-Register bits 10 thru 15, respectively.

Along with the device address, the K field and O field are transmitted to the controller. The K field, comprised of I-Register bits 4, 5 and 6, defines the class of instruction to be performed by the addressed controller. The I/O bus mnemonics for the K field are KF0- thru KF2-, corresponding to I-Register bits 4 thru 6, respectively.

The O field comprised of I-Register bits 7, 8 and 9, defines the specific function to be performed for a particular instruction class. The I/O bus mnemonics for the O field are OFO- thru OF2-, corresponding to I-Register bits 7 thru 9, respectively.

When all control lines have stablized, strobe term STRB- is generated to inform the controller to use the decoded command information to transfer data in or out, or to initiate execution of A function. The

Figure 3-1. CPU Module Functional Interface

CPU stops processing and waits (as long as 1.3 us) for a response from the device controller. If a response is received in the form of term EKO-, the CPU resumes processing and turns off the STRB- and control signal. If a response is not received within 1.3 us, the CPU can opt to assume that no response is forthcoming. If a response is not received after 2 us, the CPU will assume a nonresponse condition and performs BSP to the address specified by the second word of the I/O instruction.

The CPU also generates a 4-MHz clock signal term PCLK, for use by certain controllers. Term PCLK is synchronous with term STRB.

When the RESET switch on the control panel is pressed with the CPU in the Halt mode, system reset term SRST- is generated. Term SRST-, which is also generated during power-up and power-down sequences, resets all status flags, stops all peripheral devices and clears all controllers, leaving them ready to accept new instructions.

#### 3.3 INPUT/OUTPUT OPERATIONS

# 3.3.1 I/O Timing

The I/O bus is asynchronous in operation. A start signal, term STRB, is generated and the master clock is stopped in the CPU. When the controller responds with EKO, the master clock is restarted. This start/stop I/O timing method enables the I/O bus to be extended without communication failure, by producing variable signal delays. The extension of time however, adds directly to interrupt service time and thus decreases the number of CPU cycles or instructions that can be performed per unit of time, which may be critical.

Basic I/O timing originates in the CPU where a 4-MHz peripheral clock signal (PCLK) is derived from an 4-MHz crystal driven oscillator. The 4-MHz and 8-MHz signals are logically combined to set a strobe flip-flop during I/O machine sequence. Generation of the resulting STRB signal initiates the controller I/O sequence, as shown in Figure 3-2.

There are two I/O data transfer sequences:

- Input data transfer.

- Output data transfer.

# 3.3.2 Input Data Transfer

The input data transfer sequence is used for Word Transfer IA (WTI), Request Device Status (RDS) and Interrogate Common Interrupts (ICI) instructions. A timing diagram showing the relationship of the signals at the controller end, is shown in Figure 3-2. The input transfer is sequenced as follows:

- Control information in the from of the device address, K field and O field, is placed on the control lines at least 330 ns before STRB- is generated. The control information has therefore settled on the I/O bus and is stable when term STRB- is generated.

- Term STRB- is generated.

- Input data or status is placed on the DIB lines as soon as possible after STRB- has been received by the controller. Any delay in providing data adds directly to the I/O transfer time.

- Term EKO- is generated within 1.3 us after the activation of STRB. Term EKO- must occur on time or a simulated BSP instruction is executed. Data to be transferred is generated at least 50 ns before term EKO is brought up, to

Figure 3-2. I/O Sequence Timing at Controller

ensure reliable gating at the CPU. If the instruction being executed is a WTI in response to an interrupt, the controller interrupt line must be reset within 50 ns after the leading edge of EKO.

- Term STRB- goes false. This discontinues the gating of data out of the controller.

- Control information ends.

# 3.3.3 Output Data Transfer

The output data transfer sequence is used for word transfer out (WTO) and execute device function (EDF) instructions.

showing the relationship of the signals at the controller end, is shown in Figure 3-2. The output transfer is sequenced as follows:

- Control information in the form of the device address, K field and O field is placed on the control lines at least 330 ns before term STRB- is generated. All decoding of control signals must be accomplished within this period.

- Output data or device function information is placed on the DOB lines at least 70 ns before term STRB is generated to ensure reliable gating at the controller.

- Term STRB- is generated.

- Term EKO- is generated within 1.3 us after the activation of STRB-. Term EKO- must occur on time or a simulated BSP instruction is executed. If the instruction being executed is a WTO in response to an interrupt, terms EKO and WTO will reset the controller interrupt line. The line must be reset within 50 ns of the leading edge of term EKO.

- Term STRB- ends.

- Control information and data must remain active for at least 75 ns after the fall of STRB; this ensures reliable gating of data into the controller.

#### 3.4 INTERRUPT OPERATIONS

Program interrupts provide the capability of responding to a condition that needs immediate service without requiring the program to check the status of a peripheral device. When a controller is ready to either provide or accept data, it interrupts the main program. This causes the program to branch to the appropriate interrupt service subroutine.

A fixed memory location (Table 3-1) is assigned to each program interrupt. Each such fixed interrupt memory location contains the address of the first location of the interrupt service subroutine associated with the corresponding program interrupt.

The CPU normally accepts the interrupt at the completion of the current instruction execution, except when a BSP, a Load Interrupt Enable (LIE), a Store Interrupt Enable (SIE), or an I/O instruction is being executed at the time the interrupt is set. In any of these cases, one additional instruction is executed before the interrupt is recognized. The BSP may either be programmed or simulated via a response to an interrupt or an I/O reject. When the interrupt is recognized by the CPU, an interrupt flip-flop (of which there is one for each interrupt line) is set to prevent further interrupts on that line or lower priority lines, until the interrupt has been processed. A simulated BSP is executed to the memory location specified in the fixed interrupt memory location.

The P-Register value of the interrupted program is stored in the first location of the interrupt service routine. It points to the

Table 3-1. Interrupt Memory and Device Address and Priority

Assignment

| Interrupt                         | Memory Address<br>(Hexadecimal) | Interrupt (Hexadecimal) | Priority<br>Class |

|-----------------------------------|---------------------------------|-------------------------|-------------------|

| Internal                          | ,                               |                         |                   |

| Power Fail/Restart                | \$0A                            | 0                       | 1                 |

| Instruction Trap                  | \$0C                            | 2                       | 2                 |

| Memory Protect*                   | \$0D                            | 3                       | 3                 |

| Privileged Instruction Interrupt* | \$OE                            | 4                       | 4                 |

| External                          |                                 |                         |                   |

| I/O Interrupt*                    | \$10                            | 0                       | 5                 |

| I/O Interrupt*                    | \$11                            | 1                       | 6                 |

| I/O Interrupt*                    | \$12                            | 2                       | 7                 |

| I/O Interrupt*                    | \$13                            | 3                       | 8                 |

| I/O Interrupt*                    | \$14                            | 4                       | 9                 |